聚焦CMOS類比集成電路版圖設計領域,從版圖的基本概念、設計方法和EDA工具入手,循序漸進地介紹了CMOS類比集成電路版圖規劃、佈局、設計到驗證的全流程。

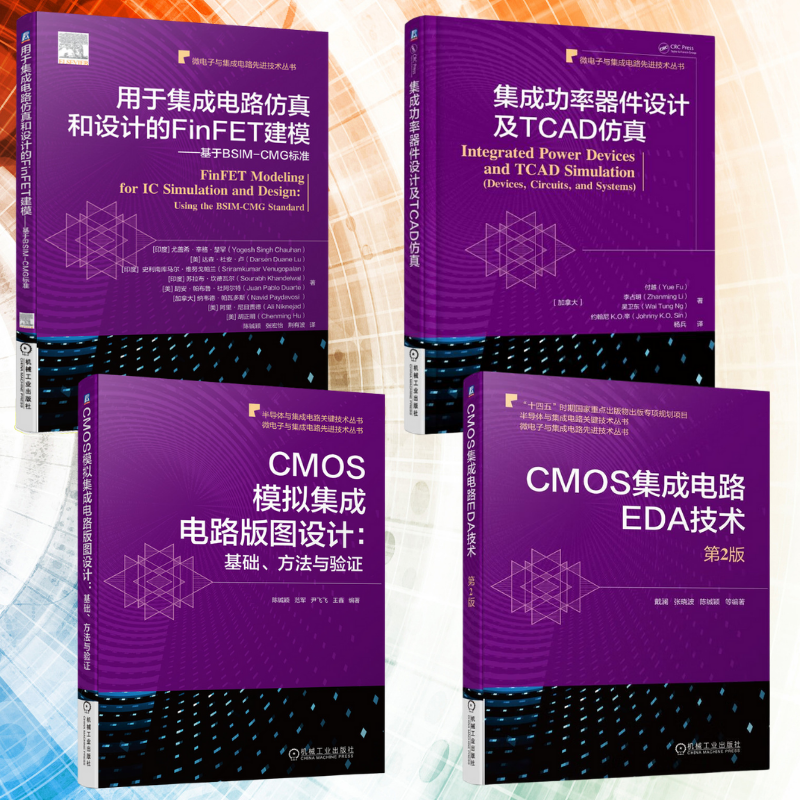

【CMOS集成電路EDA科技】

內容簡介

集成電路發展到今天,單晶片內能够集成高達百億個電晶體,在集成電路的設計中需要依靠電子設計自動化(EDA)工具進行電路模擬、綜合、版圖設計、寄生參數選取和後模擬。 EDA工具的使用可以使設計者在虛擬的電腦環境中進行早期的設計驗證,有效縮短了電路實體反覆運算驗證的時間,提高了晶片設計的成功率。 一款成功的晶片源於無數工程師成功的設計,而成功的設計在很大程度上又取決於有效、成熟的集成電路EDA設計工具。

本書面向微電子學與固體電子學專業相關的課程教學要求和積體電路設計相關的工程應用需求,以提高實際工程設計能力為目的,採取循序漸進的管道,介紹了進行CMOS積體電路設計時所需的EDA工具。 主要分為EDA設計工具概述、類比集成電路EDA科技、數位積體電路EDA科技與集成電路反向分析科技等部分。 在類比集成電路方面,依次介紹了電路設計及模擬工具Cadence Spectre、版圖設計工具Cadence Virtuoso、版圖驗證及參數選取工具Mentor Calibre在內的各種工具的基本知識和使用方法。 在數位積體電路方面,在簡單介紹硬體描述語言Verilog HDL的基礎上,介紹RTL模擬工具Modelsim、邏輯綜合工具Design Compiler、數位後端版圖工具IC Compiler和Encounter四大類設計工具。* 終對集成電路使用反向EDA科技進行全面的闡述。 書中配以電路設計實例,進一步分析各種EDA工具的設計輸入方法和技巧,形成一套完整的CMOS積體電路設計流程。

本書使讀者通過實例深刻瞭解使用CMOS集成電路EDA工具進行設計的基本流程和方法,可作為高等院校微電子學與固體電子學專業大學生與研究生集成電路EDA課程的實驗教材和輔導書,或者相關專業科技人員的自學參考書。

目錄

第2版前言

第1版前言

第1章CMOS集成電路EDA科技1

1.1CMOS集成電路EDA科技概述1

1.2CMOS類比積體電路設計流程3

1.3CMOS類比集成電路EDA工具分類5

1.4CMOS數位積體電路設計流程9

1.5CMOS數位積體電路EDA工具分類11

1.6小結13

第2章類比電路設計及模擬工具Cadence Spectre14

2.1Spectre的特點14

2.2Spectre的模擬設計方法16

2.3Spectre與其他EDA軟件的連接17

2.4Spectre的基本操作18

2.4.1Cadence Spectre啟動設定18

2.4.2Spectre主視窗和選項介紹19

2.4.3設計庫管理器介紹22

2.4.4電路圖編輯器介紹25

2.4.5類比設計環境介紹29

2.4.6波形顯示視窗介紹32

2.4.7波形小算盘介紹37

2.5Spectre庫中的基本器件42

2.5.1無源器件42

2.5.2有源器件42

2.5.3信號源43

2.6低壓差線性穩壓器的設計與模擬45

2.7高階模擬功能與實例53

2.7.1FFT模擬53

2.7.2Monte Carlo模擬59

2.8小結65

第3章版圖設計工具Cadence Virtuoso66

3.1Virtuoso介面介紹66

3.1.1視窗標題列68

3.1.2狀態列69

3.1.3功能表列69

3.1.4圖標選單77

3.1.5設計區域79

3.1.6光標和指針79

3.1.7滑鼠狀態80

3.1.8提示欄81

3.1.9層選擇視窗81

3.2Virtuoso基本操作83

3.2.1創建矩形83

3.2.2創建多邊形84

3.2.3創建路徑85

3.2.4創建標識名86

3.2.5創建器件和陣列86

3.2.6創建接觸孔88

3.2.7創建圓形圖形88

3.2.8移動命令90

3.2.9複製命令91

3.2.10拉伸命令91

3.2.11删除命令92

3.2.12合併命令92

3.2.13選擇和放弃選擇命令93

3.2.14改變層次關係命令94

3.2.15切割命令96

3.2.16旋轉命令97

3.2.17内容命令98

3.2.18分離命令99

3.3運算放大器版圖設計實例100

3.3.1NMOS電晶體版圖設計100

3.3.2運算放大器版圖設計106

3.4小結114

第4章類比版圖驗證及參數選取工具Mentor Calibre115

4.1Mentor Calibre版圖驗證工具調用115

4.1.1Virtuoso Layout Editor工具啟動115

4.1.2採用Calibre圖形介面啟動118

4.1.3採用Calibre View檢視器啟動118

4.2Mentor Calibre DRC驗證120

4.2.1Calibre DRC驗證簡介120

4.2.2Calibre DRC介面介紹122

4.2.3Calibre DRC驗證流程舉例128

4.3Mentor Calibre LVS驗證137

4.3.1Calibre LVS驗證簡介137

4.3.2Calibre LVS介面介紹138

4.3.3Calibre LVS驗證流程舉例149

4.4Mentor Calibre寄生參數選取158

4.4.1Calibre PEX驗證簡介158

4.4.2Calibre PEX介面介紹159

4.4.3Calibre PEX流程舉例169

4.5小結175

第5章硬體描述語言及模擬工具Modelsim176

5.1硬體描述語言及模擬概述176

5.2硬體描述語言與應用實例177

5.2.1硬體描述語言基礎177

5.2.2硬體描述語言應用實例185

5.2.3硬體描述語言的可綜合設計190

5.2.4硬體描述語言設計實例191

5.3數位電路模擬工具Modelsim195

5.3.1Modelsim的特點與應用196

5.3.2Modelsim的基本使用199

5.3.3Modelsim的進階使用208

5.4小結223

第6章數位邏輯綜合及Design Compiler224

6.1邏輯綜合概述224

6.1.1邏輯綜合的定義及發展歷程224

6.1.2邏輯綜合的流程225

6.2DesignCompiler簡介226

6.2.1DesignCompiler的功能226

6.2.2DesignCompiler的使用模式227

6.2.3DC-Tcl簡介228

6.3DesignCompiler綜合設計232

6.3.1啟動工具及初始環境配寘232

6.3.2綜合庫234

6.3.3DesignCompiler綜合流程235

6.4靜態時序分析與設計約束243

6.4.1靜態時序分析243

6.4.2亞穩態245

6.4.3時鐘的約束245

6.4.4輸入輸出路徑的約束247

6.4.5組合邏輯路徑的約束248

6.4.6時間預算249

6.4.7設計環境約束250

6.4.8多時鐘同步設計約束253

6.4.9非同步設計約束255

6.4.10多時鐘的時序約束256

6.5基於狀態機的交通燈綜合258

6.6小結262

第7章數位電路實體層設計工具IC Compiler263

7.1IC Compiler簡介263

7.2IC Compiler實體層設計的數據準備265

7.2.1邏輯層數據265

7.2.2實體層數據266

7.2.3設計數據266

7.3創建設計資料庫與後端數據的設定267

7.3.1邏輯庫設定267

7.3.2物理庫設定267

7.3.3其他檔案設定268

7.3.4創建設計資料庫268

7.3.5庫檔案檢查268

7.3.6網表導入268

7.3.7Tlu+檔案設定與檢查269

7.3.8電源網絡設定269

7.3.9TIE單元設定270

7.3.10導入SDC檔案並進行時序約束檢查270

7.3.11定時序優化參數271

7.4不同PVT角下綜合優化的設置方法273

7.4.1scenario的建立274

7.4.2PVT角設定274

7.5宏單元與IO佈局276

7.5.1IO佈局與晶片佈局空間創建276

7.5.2宏單元的擺放277

7.6電源網絡的設計與分析278

7.6.1設計電源和地環278

7.6.2設計電源和地條278

7.6.3連接宏單元和標準單元279

7.7標準單元的佈局與優化280

7.7.1檢查是否需要添加tap cell281

7.7.2spare cell的標識281

7.7.3檢查設計輸入檔案與約束281

7.7.4確認所有路徑已經被正確地設定281

7.8時鐘樹綜合與優化283

7.8.1綜合前的檢查283

7.8.2時鐘樹綜合設定283

7.8.3執行時鐘樹綜合覈心命令286

7.9晶片佈線與優化287

7.9.1佈線前的檢查287

7.9.2ICC佈線相關設定287

7.9.3天線效應簡介與設定289

7.9.4執行佈線命令290

7.10晶片ECO與設計檔案匯出291

7.10.1Freeze silicon ECO291

7.10.2unconstrained ECO291

7.10.3設計結果匯出292

7.11小結292

第8章數位電路實體層設計工具Encounter293

8.1Encounter工具發展歷史293

8.2Encounter設計流程介紹294

8.3數據準備295

8.3.1設計數據295

8.3.2邏輯庫數據296

8.3.3物理庫數據297

8.3.4數據準備常用的指令與流程297

8.4布圖規劃與佈局301

8.4.1布圖與IO排布301

8.4.2電源網路設計303

8.4.3標準單元的佈局與優化303

8.4.4布圖規劃與佈局常用指令與流程304

8.5時鐘樹綜合311

8.5.1時鐘樹綜合簡介311

8.5.2時鐘樹流程與優化313

8.6晶片佈線315

8.6.1晶片佈線工具簡介315

8.6.2特殊佈線315

8.6.3一般佈線316

8.6.4晶片佈線流程與優化316

8.7晶片ECO與DFM318

8.7.1ECO流程與優化318

8.7.2DFM流程與優化321

8.8小結321

第9章集成電路反向分析EDA科技322

9.1集成電路反向分析概述322

9.1.1反向分析科技的主要應用323

9.1.2反向分析科技的主要流程325

9.1.3反向分析EDA科技326

9.2電路網表選取328

9.2.1網表選取概述328

9.2.2網表選取流程331

9.2.3類比單元選取336

9.2.4數位單元選取344

9.2.5線網繪製與檢查346

9.2.6數據的導入和匯出348

9.3電路層次化分析整理351

9.3.1電路分析整理概述351

9.3.2層次化整理流程352

9.3.3類比電路的層次化整理354

9.3.4數位電路的層次化整理357

9.3.5整理數據的匯出360

9.4小結361

參考文獻362

-------------------------------------------------------------

【CMOS類比集成電路版圖設計:基礎、方法與驗證】

編輯推薦

本書依託版圖設計工具Cadence Virtuoso 617和物理驗證工具SIEMENS Calibre,從類比集成電路版圖的基本概念、方法入手,包含多個典型類比集成電路版圖的設計實例,向讀者介紹類比集成電路版圖設計的理論基礎和實用設計方法,以供從事CMOS類比集成電路版圖設計的讀者參考討論之用。

內容簡介

本書聚焦CMOS類比集成電路版圖設計領域,從版圖的基本概念、設計方法和EDA工具入手,循序漸進地介紹了CMOS類比集成電路版圖規劃、佈局、設計到驗證的全流程。 詳盡地介紹了現時主流使用的類比集成電路版圖設計和驗證工具——Cadence Virtuoso 617與SIEMENS Calibre。 同時展示了運算放大器、帶隙基準源、低壓差線性穩壓器、模/數轉換器等典型類比集成電路版圖的設計實例,並對LVS驗證中的典型案例進行了歸納和總結。 本書內容由淺入深,使讀者深刻瞭解CMOS類比集成電路版圖設計和驗證的規則、流程和基本方法,對於進行CMOS類比集成電路學習的大學生、研究生,以及這個領域的工程師,都會有一定的幫助。

目錄

前言

第1章先進集成電路器件1

1.1概述1

1.2平面全耗盡絕緣襯底上矽(FD-SOI)MOSFET4

1.2.1採用薄氧化埋層的原因5

1.2.2超薄體中的二維效應8

1.3FinFET11

1.3.1三栅以及雙栅FinFET12

1.3.2實際中的結構選擇19

1.4基於gm/ID的設計方法20

1.4.1類比集成電路的層次化設計20

1.4.2gm/ID設計方法所處的地位21

1.4.3gm/ID設計方法的優勢22

1.4.4基於Vov的設計方法23

1.4.5gm/ID設計方法詳述27

1.4.6基於gm/ID的設計實例31

第2章CMOS類比集成電路版圖基礎33

2.1CMOS類比積體電路設計流程33

2.2CMOS類比集成電路版圖定義36

2.3CMOS類比集成電路版圖設計流程37

2.3.1版圖規劃38

2.3.2版圖設計實現39

2.3.3版圖驗證40

2.3.4版圖完成41

2.4版圖設計通用規則42

2.5版圖佈局44

2.5.1對稱約束下的電晶體級佈局45

2.5.2版圖約束下的層次化佈局46

2.6版圖佈線50

2.7CMOS類比集成電路版圖匹配設計54

2.7.1CMOS工藝失配機理54

2.7.2元器件版圖匹配設計規則56

第3章Cadence Virtuoso 617版圖設計工具59

3.1Cadence Virtuoso 617介面介紹59

3.1.1Cadence Virtuoso 617 CIW介面介紹60

3.1.2Cadence Virtuoso 617 Library Manager介面介紹66

3.1.3Cadence Virtuoso 617 Library Path Editor操作介紹85

3.1.4Cadence Virtuoso 617 LayoutEditor介面介紹96

3.2Virtuoso基本操作124

3.2.1創建圓形124

3.2.2創建矩形125

3.2.3創建路徑126

3.2.4創建標識名127

3.2.5調用器件和陣列128

3.2.6創建接觸孔和通孔130

3.2.7創建環形圖形131

3.2.8移動命令132

3.2.9複製命令133

3.2.10拉伸命令134

3.2.11删除命令135

3.2.12合併命令135

3.2.13改變層次關係命令136

3.2.14切割命令138

3.2.15旋轉命令139

3.2.16内容命令140

3.2.17分離命令141

3.2.18改變形狀命令142

3.2.19版圖層擴縮命令143

第4章SIEMENS Calibre版圖驗證工具145

4.1SIEMENS Calibre版圖驗證工具簡介145

4.2SIEMENS Calibre版圖驗證工具調用145

4.2.1採用Virtuoso Layout Editor內嵌管道啟動146

4.2.2採用Calibre圖形介面啟動147

4.2.3採用Calibre View檢視器啟動149

4.3SIEMENS Calibre DRC驗證151

4.3.1Calibre DRC驗證簡介151

4.3.2Calibre nmDRC介面介紹153

4.3.3Calibre nmDRC驗證流程舉例159

4.4SIEMENS Calibre nmLVS驗證170

4.4.1Calibre nmLVS驗證簡介170

4.4.2Calibre nmLVS介面介紹170

4.4.3Calibre nmLVS驗證流程舉例183

4.5SIEMENS Calibre寄生參數選取(PEX)194

4.5.1Calibre PEX驗證簡介194

4.5.2Calibre PEX介面介紹194

4.5.3Calibre PEX流程舉例204

第5章Calibre驗證檔案213

5.1Virtuoso Techfile214

5.1.1Virtuoso Techfile內容214

5.1.2修改示例215

5.2Virtuoso Layer Map217

5.2.1Virtuoso Layer Map內容217

5.2.2示例:Virtuoso Layer Map修改方法218

5.3Virtuoso Symbol CDF218

5.3.1Virtuoso Symbol CDF內容219

5.3.2示例:Virtuoso參數修改方法219

5.4SVRF語言221

5.4.1SVRF基本符號使用222

5.4.2SVRF基本math function222

5.4.3SVRF基本格式222

5.4.4Layer Operations運算輸出224

5.5DRC rule225

5.5.1DRC rule內容225

5.5.2DRC rule主要operation226

5.5.3DRC rule驗證方法227

5.5.4修改示例227

5.6LVS(PEX)規則230

5.6.1LVS rule內容230

5.6.2LVS rule器件定義231

5.6.3LVS rule驗證方法232

5.6.4示例:pdio18e2r LVS rule添加方法232

第6章CMOS類比集成電路版圖設計與驗證流程234

6.1設計環境準備234

6.2單級跨導放大器電路的建立和前模擬240

6.3跨導放大器版圖設計251

6.4跨導放大器版圖驗證與參數選取262

6.5跨導放大器電路後模擬279

6.6輸入輸出單元環設計285

6.7主體電路版圖與輸入輸出單元環的連接293

6.8匯出GDSII檔案298

第7章運算放大器的版圖設計301

7.1運算放大器基礎301

7.2運算放大器的基本特性和分類302

7.2.1運算放大器的基本特性302

7.2.2運算放大器的性能參數303

7.2.3運算放大器的分類307

7.3單級折疊共源共栅運算放大器的版圖設計312

7.4兩級全差分密勒補償運算放大器的版圖設計317

7.5電容—電壓轉換電路版圖設計322

第8章帶隙基準源與低壓差線性穩壓器的版圖設計329

8.1帶隙基準源的版圖設計329

8.1.1帶隙基準源基本原理329

8.1.2帶隙基準源版圖設計實例335

8.2低壓差線性穩壓器的版圖設計339

8.2.1低壓差線性穩壓器的基本原理340

8.2.2低壓差線性穩壓器版圖設計實例342

第9章模/數轉換器的版圖設計347

9.1性能參數347

9.1.1靜態參數348

9.1.2動態特性351

9.1.3功耗名額353

9.1.4抖動353

9.2模/數轉換器的結構及版圖設計354

9.2.1快閃型模/數轉換器(Flash ADC)354

9.2.2快閃型模/數轉換器版圖設計357

9.2.3流水線模/數轉換器基礎(Pipelined ADC)363

9.2.4流水線模/數轉換器版圖設計371

9.2.5逐次逼近模/數轉換(SuccessiveApproximationADC)373

9.2.6逐次逼近模/數轉換器版圖設計377

9.2.7Sigma-Delta模/數轉換器381

9.2.8Sigma-Delta調製器版圖設計398

第10章Calibre LVS常見錯誤解析400

10.1LVS錯誤對話方塊(RVE對話方塊)400

10.2誤連接408

10.3短路410

10.4斷路411

10.5違反工藝原理412

10.6漏標416

10.7元件參數錯誤417

參考文獻419

-------------------------------------------------------------

【用於集成電路模擬和設計的FinFET建模基於BSIM-CMG標準】

內容簡介

隨著集成電路工藝特徵尺寸進入28nm以下節點,傳統的平面MOSFET結構已不再適用,新型的三維電晶體(FinFET)結構逐漸成為摩爾定律得以延續的重要保證。 本書從三維結構的原理、物理效應入手,詳細討論了FinFET緊湊模型(BSIM-CMG)產生的背景、原理、參數以及實現方法; 同時討論了在類比和射頻積體電路設計中所採用的模擬模型。 本書避開了繁雜的公式推導,而進行了更為直接的機理分析,力求使得讀者從工藝、器件層面理解BSIM-CMG的特點和使用方法。

本書可以作為微電子學與固體電子學、電子資訊工程等專業高年級大學生、研究生的專業教材和教師參攷用書,也可以作為工程師進行集成電路模擬的FinFET模型手册。

目錄

譯者序

原書前言

第1章FinFET——從器件概念到

標準的緊湊模型1

1121世紀MOSFET短溝道效應產生

的原因1

12薄體MOSFET理論3

13FinFET和一條新的MOSFET縮放

路徑3

14超薄體場效應電晶體4

15FinFET緊湊模型——FinFET工藝

與積體電路設計的橋樑5

16第一個標準緊湊模型BSIM

簡史6

17覈心模型和實際器件模型7

18符合工業界標準的FinFET

緊湊模型9

參考文獻10

第2章基於類比和射頻應用的

緊湊模型11

21概述11

22重要的緊湊模型名額12

23類比電路名額12

231靜態工作點12

232幾何尺寸縮放16

233變數模型17

234本征電壓增益19

235速度:組織增益頻率24

236雜訊27

237線性度和對稱性28

238對稱性35

24射頻電路名額36

241二埠參數36

242速度需求38

243非准靜態模型46

244雜訊47

245線性度53

25總結57

參考文獻57

第3章FinFET覈心模型59

31雙栅FinFET的覈心模型60

32統一的FinFET緊湊模型67

第3章附錄詳細的表面電動勢

模型72

3A1連續啟動函數73

3A2四次修正反覆運算:實現和

評估75

參考文獻80

第4章溝道電流和實際器件

效應83

41概述83

42閾值電壓滾降83

43亞閾值斜率退化89

44量子力學中的Vth校正90

45垂直場遷移率退化91

46漏極飽和電壓Vdsat92

461非本征示例(RDSMOD=

1和2)92

462本征示例(RDSMOD=0)94

47速度飽和模型97

48量子效應98

481有效寬度模型99

482有效氧化層厚度/有效

電容101

483電荷質心累積計算101

49橫向非均勻摻雜模型102

410體FinFET的體效應模型

(BULKMOD=1)102

411輸出電阻模型102

4111溝道長度調製103

4112漏致勢壘降低105

412溝道電流106

參考文獻106

第5章洩漏電流108

51弱反型電流109

52栅致源極洩漏及栅致漏極

洩漏110

521BSIM-CMG中的栅致漏極泄

漏/栅致源極洩漏公式112

53柵極氧化層隧穿113

531BSIM-CMG中的柵極氧

化層隧穿公式113

532在耗盡區和反型區中的

柵極-體隧穿電流114

533積累中的柵極-體隧

穿電流115

534反型中的柵極-溝道隧

穿電流117

535柵極-源/漏極隧穿電流118

54碰撞電離119

參考文獻120

第6章電荷、電容和非准靜態

效應121

61終端電荷121

611柵極電荷121

612漏極電荷123

613源極電荷124

62跨容124

63非准靜態效應模型126

631弛豫時間近似模型126

632溝道誘導柵極電阻

模型128

633電荷分段模型128

參考文獻132

第7章寄生電阻和電容133

71FinFET器件結構和符號

定義134

72FinFET中與幾何尺寸有關

的源/漏極電阻建模137

721接觸電阻137

722擴散電阻139

723擴展電阻142

73寄生電阻模型驗證143

731TCAD模擬設定144

732器件優化145

733源/漏極電阻選取146

734討論150

74寄生電阻模型的應用考慮151

741物理參數152

742電阻分量152

75柵極電阻模型153

76FinFET寄生電容模型153

761寄生電容分量之間的

聯系153

762二維邊緣電容的推導154

77三維結構中FinFET邊緣電容

建模:CGEOMOD=2160

78寄生電容模型驗證161

79總結165

參考文獻166

第8章雜訊168

81概述168

82熱雜訊168

83閃爍雜訊170

84其他雜訊分量173

85總結174

參考文獻174

第9章結二極體I-V和C-V

模型175

91結二極體電流模型176

911反偏附加洩漏模型179

92結二極體電荷/電容模型181

921反偏模型182

922正偏模型183

參考文獻186

第10章緊湊模型的基準

測試187

101漸近正確性原理187

102基準測試188

1021弱反型區和强反型區的物理

行為驗證188

1022對稱性測試191

1023緊湊模型中電容的互易性

測試194

1024自熱效應模型測試194

1025熱雜訊模型測試196

參考文獻196

第11章BSIM-CMG模型參數

選取197

111參數選取背景197

112BSIM-CMG模型參數選取

策略198

113總結206

參考文獻206

第12章溫度特性208

121電晶體特性208

1211帶隙問題特性208

1212NC、Vbi和 Φ B的溫度

特性209

1213本征載流子濃度的溫度

特性209

122閾值電壓的溫度特性209

1221漏致勢壘降低的溫度

特性210

1222體效應的溫度特性210

1223亞閾值擺幅210

123遷移率的溫度特性210

124速度飽和的溫度特性211

1241非飽和效應的溫度

特性211

125洩漏電流的溫度特性212

1251柵極電流212

1252栅致漏/源極洩漏212

1253碰撞電離212

126寄生源/漏極電阻的溫度

特性212

127源/漏極二極體的溫度特性213

1271直接電流模型213

1272電容215

1273陷阱輔助隧穿電流215

128自熱效應217

129驗證範圍218

1210量測數據的模型驗證218

參考文獻220

附錄221

附錄A參數列表221

A1模型控制器221

A2器件參數222

A3工藝參數223

A4基本模型參數224

A5幾何相關寄生參數235

A6溫度相關性和自熱參數236

A7變數模型參數238

-------------------------------------------------------------

【集成功率器件設計及TCAD模擬】

內容簡介

《集成功率器件設計及TCAD仿真》從電力電子到功率集成電路(PIC)、智慧功率科技、器件等方面給電源管理和半導體產業提供了一個完整的描述。 《集成功率器件設計及TCAD仿真》不僅介紹了集成功率半導體器件,如橫向雙擴散金屬氧化物半導體場效應電晶體(LDMOSFET)、橫向絕緣栅雙極型電晶體(LIGBT)和超結LDMOSFET的內部物理現象,還對電源管理系統進行了一個簡單的介紹。 《集成功率器件設計及TCAD仿真》運用電腦輔助設計科技(TCAD)模擬實例講解集成功率半導體器件的設計,代替抽象的理論處理和令人生畏的方程,並且還探討了下一代功率器件,如氮化鎵高電子遷移率功率電晶體(GaN功率HEMT)。 《集成功率器件設計及TCAD仿真》內容有助於填補功率器件工程和電源管理系統之間的空白。 書中包括智慧PIC的一個典型的工藝流程以及很難在其他同類書中找到的技術開發組織圖,通過對本書的閱讀,可以使學生和年輕的工程師在功率半導體器件領域領先一步。

目錄

譯者序

原書前言

作者簡介

第1章電力電子,可以實現綠色的科技1

1.1電力電子介紹1

1.2電力電子的發展歷程3

1.3DC/DC變換器4

1.4線性穩壓器4

1.5開關電容DC/DC變換器(電荷泵)5

1.6開關模式DC/DC變換器6

1.7線性穩壓器、電荷泵和開關調節器的比較8

1.8非隔離DC/DC開關變換器的拓撲結構8

1.8.1Buck變換器9

1.8.2Boost變換器11

1.8.3Buck-boost變換器12

1.8.4Cuk變換器14

1.8.5非隔離式變換器額外的話題14

1.9隔離的開關變換器拓撲結構16

1.9.1反激式變換器16

1.9.2正激式變換器17

1.9.3全橋變換器18

1.9.4半橋變換器19

1.9.5推挽變換器20

1.9.6隔離DC/DC變換器其他話題20

1.9.7隔離DC/DC變換器拓撲結構的比較22

1.10SPICE電路模擬22

1.11對於電池供電器件的電源管理系統23

1.12小結24

第2章功率變換器和電源管理晶片25

2.1用於VLSI電源管理的動態電壓調節25

2.2集成的DC/DC變換器27

2.2.1分段的輸出級29

2.2.2一個輔助級的瞬態抑制32

2.3小結36

第3章半導體產業和超摩爾定律37

3.1半導體產業37

3.2半導體產業的歷史38

3.2.1一個簡要的時間表38

3.2.2八叛逆38

3.2.3半導體產業的歷史路線圖39

3.3半導體產業的食物鏈金字塔40

3.3.1第1層:晶圓和EDA工具41

3.3.2第2層:器件工程42

3.3.3第3層:IC設計42

3.3.4第4層:製造、封裝和測試43

3.3.5第5層:系統和軟件43

3.3.6第6層:市場行銷44

3.4電晶體公司45

3.5超摩爾定律46

第4章智慧功率IC科技49

4.1智慧功率IC科技基礎49

4.2智慧功率IC科技:歷史展望50

4.3智慧功率IC科技:產業展望52

4.3.1智慧功率IC科技的工程組52

4.3.2智慧功率IC技術開發流程55

4.3.3計畫階段56

4.3.4工藝集成和器件設計57

4.3.5布圖、投片、製造和測試58

4.3.6可靠性和標準59

4.3.7現時智慧功率科技的概述60

4.4智慧功率IC科技:科技展望61

4.4.1智慧功率科技中的器件62

4.4.2智慧功率IC科技的設計考慮62

4.4.3隔離方法65

第5章TCAD工藝模擬介紹67

5.1概述67

5.2網格設定和初始化67

5.3離子注入69

5.3.1分析模型70

5.3.2多層注入71

目錄Ⅸ

5.3.3MonteCarlo類比71

5.4澱積72

5.5氧化73

5.5.1幹氧氧化73

5.5.2濕氧氧化74

5.5.3氧化模型74

5.6刻蝕76

5.7擴散77

5.7.1擴散機制78

5.7.2擴散模型79

5.8分凝80

5.9工藝模擬器模型的校準83

5.103DTCAD工藝模擬介紹84

5.11GPU模擬85

第6章TCAD器件模擬介紹87

6.1概述87

6.2器件模擬基礎87

6.2.1漂移-擴散模型87

6.2.2離散化88

6.2.3Newton方法89

6.2.4初始猜測和自我調整偏置步長89

6.2.5收斂問題90

6.2.6邊界條件91

6.2.7瞬態模擬93

6.2.8網格問題93

6.3物理模型93

6.3.1載流子統計94

6.3.2雜質的不完全電離94

6.3.3重摻雜效應94

6.3.4SRH和Auger複合94

6.3.5雪崩擊穿和碰撞電離95

6.3.6載流子遷移率101

6.3.7熱和自加熱106

6.3.8帶隙變窄效應107

6.4AC分析107

6.4.1引言107

6.4.2基本的公式108

6.4.3在TCAD中的AC分析110

Ⅹ集成功率器件設計及TCAD模擬

6.5在TCAD模擬中的陷阱模型111

6.5.1陷阱電荷的狀態111

6.5.2陷阱動力學112

6.6量子隧穿115

6.6.1功率器件中量子隧穿的重要性115

6.6.2TCAD模擬的基本隧穿理論116

6.6.3隧穿的非平衡Green函數的介紹118

6.7器件模擬器模型的校準119

第7章功率IC工藝流程的TCAD模擬120

7.1概述120

7.2一個類比的功率IC工藝流程120

7.2.1工藝流程步驟120

7.2.2類比的工藝流程的結構視圖121

7.3智慧功率IC工藝流程類比122

7.3.1P+襯底122

7.3.2N型掩埋層123

7.3.3外延層生長和深N連接125

7.3.4高壓雙阱127

7.3.5N-LDMOS的P型體注入128

7.3.6有源區面積/淺溝槽隔離(STI)129

7.3.7N阱和P阱134

7.3.8低壓雙阱135

7.3.9厚栅氧層和薄栅氧層136

7.3.10多晶栅139

7.3.11NLDD和PLDD139

7.3.12側牆141

7.3.13NSD和PSD142

7.3.14後端工序144

第8章集成功率半導體器件的TCAD模擬150

8.1PN結二極體150

8.1.1PN結基礎150

8.1.2在平衡時的橫向PN結二極體151

8.1.3正向導通(導通態)153

8.1.4一個PN結二極體的反向偏置156

8.1.5具有NBL的橫向PN結二極體156

8.1.6PN結二極體的擊穿電壓增强158

8.1.7反向恢復166

8.1.8Schottky二極體169

目錄Ⅺ

8.1.9Zener二極體170

8.1.10PN結二極體的小訊號模型173

8.2雙極結型電晶體174

8.2.1NPN型BJT的基本工作原理175

8.2.2NPN型BJT的擊穿178

8.2.3BJT的I-V曲線族182

8.2.4Kirk效應182

8.2.5BJT熱失控和二次擊穿的模擬186

8.2.6BJT的小訊號模型和截止頻率的模擬188

8.3LDMOS191

8.3.1擊穿電壓的提高191

8.3.2LDMOS中的寄生NPNBJT220

8.3.3LDMOS的導通電阻222

8.3.4LDMOS的閾值電壓226

8.3.5LDMOS的輻照加固設計227

8.3.6LDMOS的I-V曲線族228

8.3.7LDMOS的自加熱230

8.3.8LDMOS的寄生電容231

8.3.9LDMOS的栅電荷234

8.3.10LDMOS非鉗比特感應開關(UIS)235

8.3.11LDMOS的簡潔模型236

第9章集成的功率半導體器件的3DTCAD類比238

9.13D器件的佈局效應238

9.2LIGBT的3D模擬241

9.2.1關於LIGBT241

9.2.2分段陽極LIGBT241

9.2.3分段陽極LIGBT3D工藝模擬244

9.2.4分段陽極LIGBT的3D器件模擬246

9.3超結LDMOS254

9.3.1基本概念254

9.3.2超結LDMOS的結構261

9.3.3超結LDMOS的3D模擬261

9.3.4超結LDMOS的3D器件模擬264

9.3.5一個具有相同的N漂移區摻雜的標準LDMOS的3D模擬265

9.3.6一個N漂移區摻雜降低的標準LDMOS的3D模擬265

9.3.7超結LDMOS和標準LDMOS的比較266

9.4超結功率FinFET267

9.4.1超結功率FinFET的工藝流程269

Ⅻ集成功率器件設計及TCAD模擬

9.4.2超結功率FinFET的量測結果270

9.4.3超結功率FinFET的3D模擬271

9.5大的互連模擬273

9.5.1大的互連的3D工藝模擬275

9.5.2大的互連的3D器件模擬279

第10章GaN器件介紹281

10.1化合物資料與矽281

10.2GaN器件的襯底資料282

10.3Ⅲ-氮族纖鋅礦結構的極化特性283

10.3.1微觀偶極子與極化向量283

10.3.2晶體結構與極化284

10.3.3零淨極化的理想c0/a0比284

10.4AlGaN/GaN異質結287

10.4.1具有固定鋁摩爾分數的能帶圖288

10.4.2具有一個固定的AlGaN層厚度的能帶圖289

10.4.3具有摻雜的AlGaN或GaN層的AlGaN/GaN結構291

10.4.4具有金屬接觸的AlGaN/GaN結構292

10.5在AlGaN/GaN結構中的陷阱293

10.6一個簡單的AlGaN/GaNHEMT294

10.6.1器件結構294

10.6.2GaNHEMT的ID-VG曲線296

10.6.3小結297

10.7GaN功率HEMT例子Ⅰ298

10.7.1器件結構298

10.7.2GaN資料的碰撞電離係數300

10.7.3GaNHEMT器件的擊穿模擬300

10.8GaN功率HEMT範例Ⅱ301

10.9GaNHEMT器件的柵極漏電流的模擬302

10.9.1器件結構302

10.9.2模型和模擬設定303

10.9.3柵極洩漏電流模擬305

10.10化合物電晶體電力應用的市場前景306

附錄A載流子統計308

附錄B載流子統計309

附錄C陷阱動力學和AC分析320

NT$1499

【DeepSeek藍寶書+紅寶書】(套裝3册)

NT$1399

【低空無人機集羣科技】

NT$1999

無人機系統成像與感知:【控制與效能+部署與應用】

NT$1799

【超大規模集成電路物理設計:從圖分割到時序收斂】+【專用集成電路低功耗入門:分析、科技和規範】

NT$1799

【電晶體幹法刻蝕科技】

NT$1399

【車規級晶片科技】

NT$2750

【電晶體幹法刻蝕科技:原子層工藝】

NT$1999

【質子交換膜燃料電池基礎與效能計算】+【質子交換膜燃料電池混合動力、故障診斷和預測】

NT$1800

【MEMS三維晶片集成科技】+【電晶體先進光刻理論與科技】

NT$3300

集成電路系列:【矽通孔三維封裝技術】+【功率電晶體封裝技術】+【集成電路先進封裝資料】+【集成電路系統級封裝】

NT$2700

電子工程師:【元器件應用寶典】+【九大系統電路識圖寶典】+【電路板技能速成寶典】

NT$3000

新概念類比電路:【電晶體、運放和負反饋+頻率特性和濾波器+信號處理和源電路】

NT$3300

美國機械工程手冊第29版:【基礎卷】+【零部件卷】(套裝兩册,質重4公斤)

NT$2250

【納米集成電路FinFET器件物理與模型】+【氮化鎵功率晶體管 器件、電路與應用】+【半導體工程導論】

NT$3150

【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】+【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】

NT$2350

【功率電晶體基礎與工藝精講(第2版)】+【電晶體製造設備基礎與構造精講(第3版)】+【電晶體制造技術基礎精講(第4版)】

NT$2500

【繞射極限附近的光刻工藝】+【計算光刻與版圖優化】+【雷射熱敏光刻:原理與方法】

NT$1800

機械設計(原書第5版)

NT$2050

【代碼大全2】(全新中文紀念版)

NT$1799

【工業電路板晶片級維修從入門到精通】+【工業電路板晶片級維修技能全圖解】+【工業電路板晶片級維修彩色圖解】(全彩)